### Abstract

In modern digital system designs, energy consumption is emerging as a key issue, especially for battery-powered portable systems. Dynamic voltage scaling (DVS), which adjusts dynamically the processor clock frequency and supply voltage, is one of the most effective approaches in reducing the energy consumptions of digital systems because energy consumption has a quadratic dependency on the supply voltage. However, this lead to a performance degradation of the system because the maximum allowable clock frequency is proportional to supply voltage. For hard real-time systems where timing constraints must be strictly satisfied, this energy-performance tradeoff makes it more challenging to adjust the supply voltage dynamically so that the energy consumption is minimized while not violating the timing requirements.

In this dissertation, clock and voltage scheduling algorithms for realtime applications are addressed. We propose a voltage scheduling model within task boundary, called IntraDVS. The clock frequency and supply voltage is controlled according to the execution flow of a task within the task boundary. By fully exploiting all the slack times, a scheduled program by the proposed technique always completes its execution near the deadline, thus achieving a high energy reduction ratio.

First, we formulate the IntraDVS problem and propose an IntraDVS al-

gorithm based on static timing analysis. It exploits the information about

worst-case execution path. We also introduce a software tool that auto-

matically converts a DVS-unaware program into an equivalent low-energy

program using the IntraDVS techniques.

Second, two techniques to improve the energy performance of the In-

traDVS are introduced. One is to use profile information to optimize the

voltage scheduling for the average-case execution path. The other is to use

data flow analysis technique to optimize the locations of scaling points.

Third, how to cooperate with the OS-level voltage scheduler is described.

Though IntraDVS exploits all slack times within a task boundary, there are

cases where it is better to transfer slack times to following tasks. We propose

hybrid DVS algorithms, which determine the slack distribution observing

the current system status.

Each algorithm proposed in this dissertation is evaluated in terms of

energy consumption using simulations and measurements. We compare

our voltage scheduling algorithms with other task-level or OS-level volt-

age scheduling algorithms. The experiments show the efficiencies of the

newly proposed voltage scheduling techniques.

**Keywords**: dynamic voltage scaling, variable-voltage processor, real-time

systems, power management, low-power design

Student Number: 2000-30298

ii

# Contents

| $\mathbf{A}$ | bstra | act                               | i   |

|--------------|-------|-----------------------------------|-----|

| $\mathbf{G}$ | lossa | ry                                | xii |

| 1            | Intr  | $\operatorname{roduction}$        | 1   |

|              | 1.1   | Motivation                        | 1   |

|              | 1.2   | Dissertation Goals                | 5   |

|              | 1.3   | Contributions                     | 5   |

|              | 1.4   | Dissertation Structure            | 7   |

| <b>2</b>     | Bac   | ckground                          | 9   |

|              | 2.1   | Real-Time Systems                 | 9   |

|              | 2.2   | Dynamic Voltage Scaling           | 11  |

|              |       | 2.2.1 Power and Energy            | 11  |

|              |       | 2.2.2 Variable-Voltage Processors | 14  |

|   | 2.3  | Related Works                                    | 6  |

|---|------|--------------------------------------------------|----|

|   |      | 2.3.1 InterDVS Algorithms                        | 6  |

|   |      | 2.3.2 IntraDVS Algorithms                        | 9  |

| 3 | Intr | a-Task Voltage Scheduling Framework 2            | 1  |

|   | 3.1  | Basic Idea                                       | 21 |

|   | 3.2  | Problem Modeling                                 | 24 |

|   | 3.3  | Voltage Scheduling Using Reference Path          | 29 |

| 4 | Intr | aDVS Using Static Timing Analysis 3:             | 2  |

|   | 4.1  | RWEP-based IntraDVS Algorithm                    | 32 |

|   | 4.2  | Selection of Voltage Scaling Edges               | 7  |

|   |      | 4.2.1 B-type Voltage Scaling Edges               | 8  |

|   |      | 4.2.2 L-type Voltage Scaling Edges 4             | 1  |

|   |      | 4.2.3 VSEs in Loops or Functions 4               | 3  |

|   | 4.3  | Code Transformation                              | 4  |

|   | 4.4  | Overall Selection Algorithm                      | 5  |

|   | 4.5  | Experiments                                      | 9  |

|   |      | 4.5.1 Experiments with Artificial Workloads 4    | 9  |

|   |      | 4.5.2 Experiments with Real Applications 5       | 52 |

|   |      | 4.5.3 Experiments on a Real DVS-enabled System 5 | 57 |

|   |     | 4.5.4   | Comparisons of IntraDVS Algorithms           | 62  |

|---|-----|---------|----------------------------------------------|-----|

|   |     | 4.5.5   | Comparisons of InterDVS and IntraDVS         | 63  |

|   | 4.6 | IntraD  | OVS for Soft Real-Time Tasks                 | 66  |

|   |     | 4.6.1   | QoS-driven IntraDVS                          | 66  |

|   |     | 4.6.2   | Experiments                                  | 69  |

| 5 | Ene | ergy-Ef | ficiency Improvement Techniques for IntraDVS | 73  |

|   | 5.1 | IntraD  | OVS Using Profile Information                | 73  |

|   |     | 5.1.1   | Motivation                                   | 73  |

|   |     | 5.1.2   | Guaranteeing Safeness                        | 80  |

|   |     | 5.1.3   | Comparisons of RWEP-based IntraDVS and RAEP- |     |

|   |     |         | based IntraDVS algorithms                    | 85  |

|   |     | 5.1.4   | Experiments                                  | 87  |

|   | 5.2 | IntraD  | OVS Using Data Flow Analysis                 | 90  |

|   |     | 5.2.1   | Motivation                                   | 90  |

|   |     | 5.2.2   | Single-Step Look-ahead IntraDVS              | 92  |

|   |     | 5.2.3   | Multi-Step Look-ahead IntraDVS               | 95  |

|   |     | 5.2.4   | Further Enhancements                         | 100 |

|   |     | 5.2.5   | Experiments                                  | 103 |

| 6 | Coc | perati  | ve IntraDVS under OS-Level Voltage Scheduler | 108 |

|                           | 6.1   | Motiva               | tion                                            | 108 |

|---------------------------|-------|----------------------|-------------------------------------------------|-----|

|                           | 6.2   | Hybrid               | DVS algorithms                                  | 110 |

|                           | 6.3   | Experi               | ments                                           | 113 |

| 7                         | Con   | clusior              | ıs                                              | 116 |

|                           | 7.1   | Summa                | ary and Contributions                           | 116 |

|                           | 7.2   | Future               | Works                                           | 119 |

|                           |       | 7.2.1                | IntraDVS Using Frequency-Aware Timing Analysis  | 119 |

|                           |       | 7.2.2                | IntraDVS Using Run-Time Monitoring              |     |

|                           |       | 7.2.3                | IntraDVS Considering Static Power               | 122 |

|                           |       | 7.2.4                | Inter-Task DVS Using Intra-Task Slack Detection | 123 |

| Bi                        | bliog | graphy               |                                                 | 124 |

| $\mathbf{A}_{\mathbf{I}}$ | ppen  | $\operatorname{dix}$ |                                                 | 132 |

|                           | А. Г  | OVS Har              | dware Platforms                                 | 132 |

|                           | В. А  | utomat               | ic Voltage Scaler                               | 139 |

# List of Figures

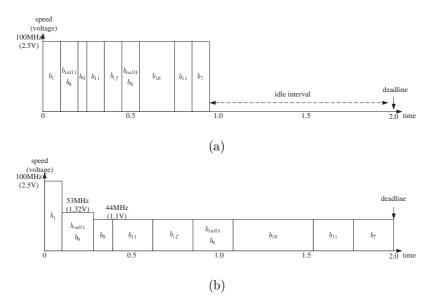

| 3.1 | An example program $P$ : (a) an example real-time program       |    |

|-----|-----------------------------------------------------------------|----|

|     | with the 2 sec deadline and (b) its CFG representation $G_P$ .  | 23 |

| 3.2 | The heuristic search algorithm for IntraDVS problem             | 28 |

| 4.1 | A RWEP-based CFG $G_P^{RWEP}$                                   | 33 |

| 4.2 | The changes of $C_{RWEC}(t)$ over different speed scaling algo- |    |

|     | rithms: (a) no IntraDVS and (b) RWEP-based IntraDVS             | 35 |

| 4.3 | Speed and voltage changes: (a) without IntraDVS and (b)         |    |

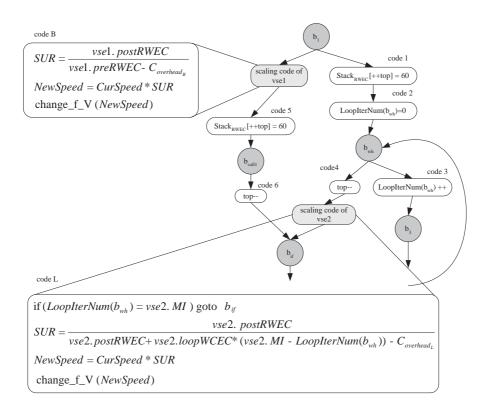

|     | with the RWEP-based IntraDVS                                    | 38 |

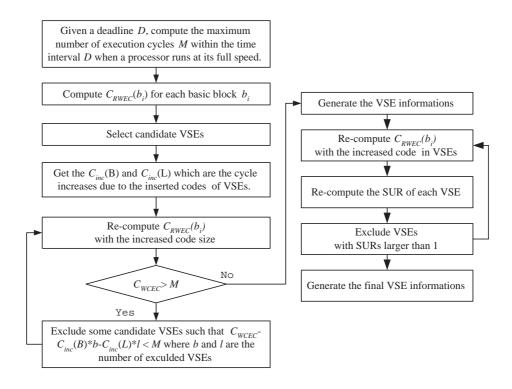

| 4.4 | Code generation for VSEs                                        | 46 |

| 4.5 | Overall VSE selection algorithm                                 | 48 |

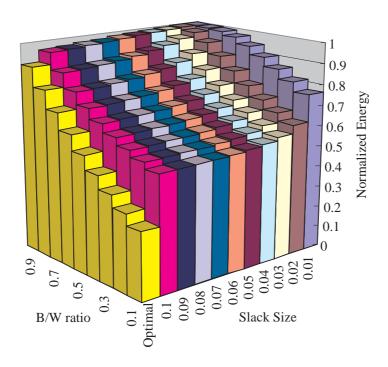

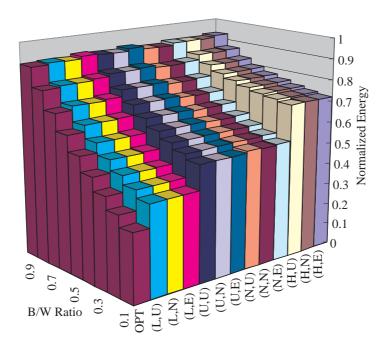

| 4.6 | Normalized energy consumptions of the RWEP-based IntraDVS $$    |    |

|     | (varying the B/W ratio and the slack size)                      | 51 |

| 4.7 | Normalized energy consumptions of the RWEP-based IntraDVS $$    |    |

|     | (varying the B/W ratio and the slack distribution)              | 52 |

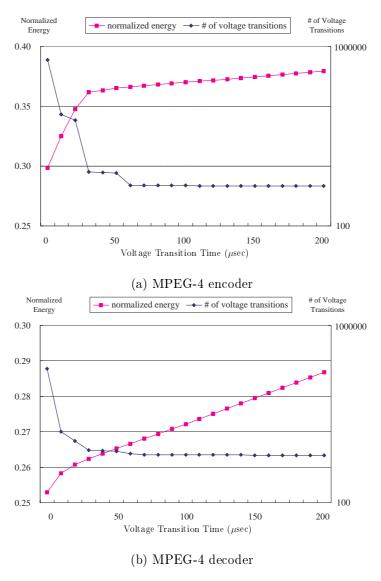

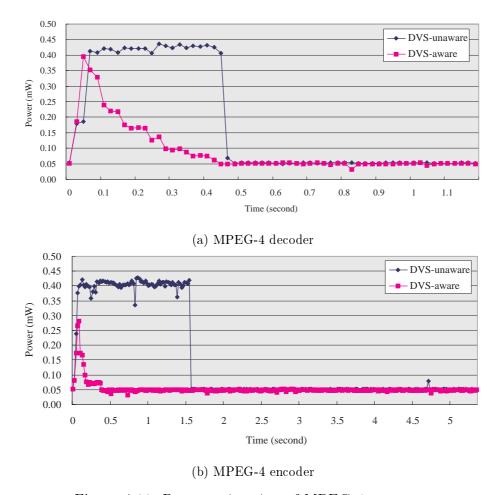

| 4.8  | transitions of the AVS-converted MPEG-4 encoder and decoder programs                                                     | 55 |

|------|--------------------------------------------------------------------------------------------------------------------------|----|

| 4.9  | Normalized energy consumptions of the on-line and off-line speed assignment methods (varying the threshold value)        | 56 |

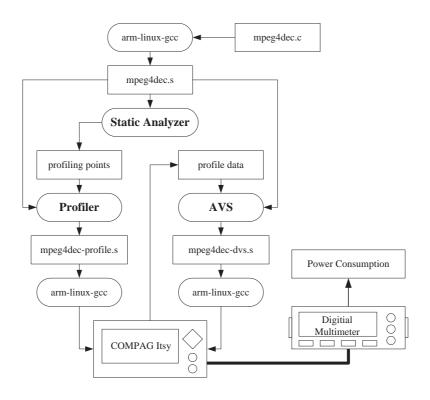

| 4.10 | The experiment environments for Itsy platform                                                                            | 58 |

| 4.11 | Power estimation of MPEG-4 program                                                                                       | 61 |

| 4.12 | Energy consumption ratio of IntraDVS-P and IntraDVS-S                                                                    | 63 |

| 4.13 | Comparison of InterDVS and IntraDVS in multi-task environments                                                           | 65 |

| 4.14 | Comparison of InterDVS and IntraDVS in different task sets.                                                              | 67 |

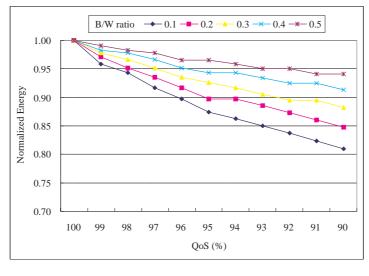

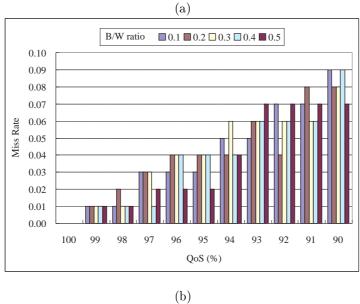

| 4.15 | The changes of $C_{RWEC}(t)$ over different speed scaling algorithms: (a) Original IntraDVS and (b) QoS-driven IntraDVS. | 70 |

| 4.16 | The experimental results: (a) Energy Consumption and (b) Deadline Miss                                                   | 72 |

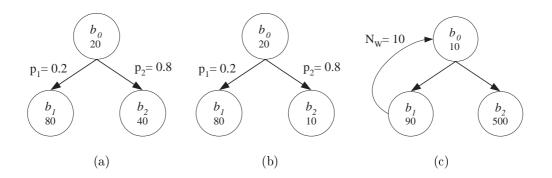

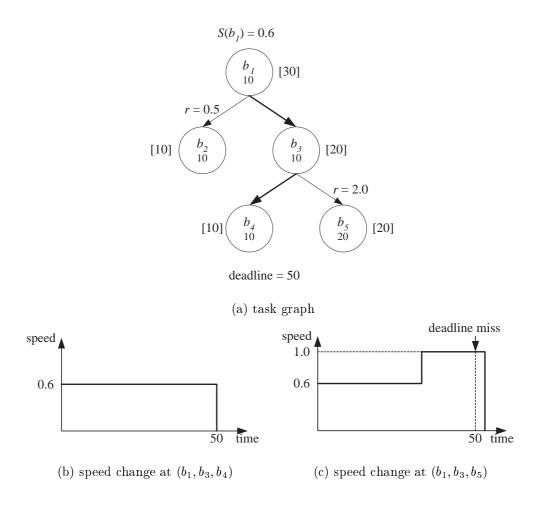

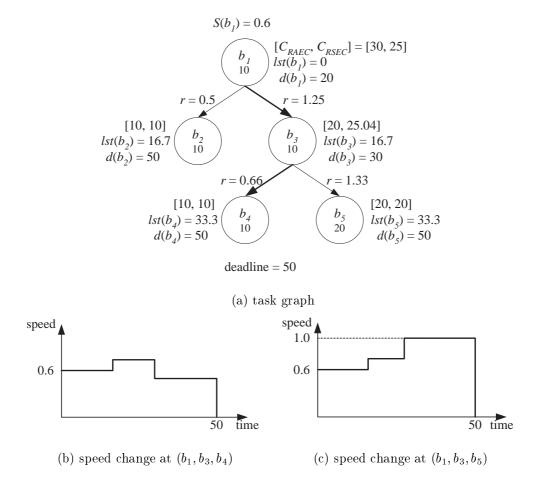

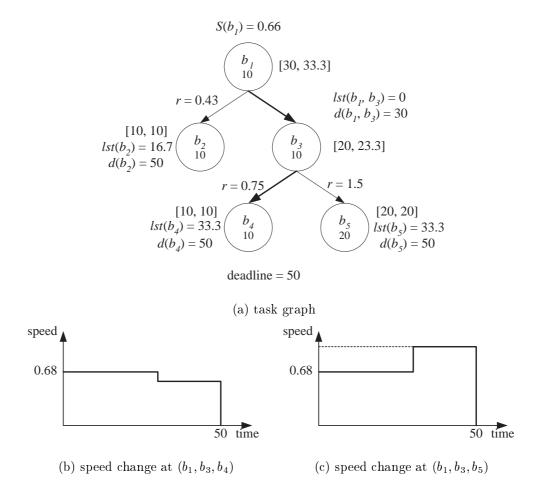

| 5.1  | Example task graphs for RAEP-based IntraDVS                                                                              | 74 |

| 5.2  | A RAEP-based CFG $G_P^{RAEP}$                                                                                            | 79 |

| 5.3  | Speed and voltage changes by the RAEP-based IntraDVS                                                                     | 79 |

| 5.4  | The changes of $C_{RAEC}(t)$ over RAEP-based IntraDVS                                                                    | 80 |

| 5.5  | Pure RAEP-based IntraDVS                                                                                                 | 83 |

| 5.6  | Safe RAEP-based IntraDVS                                                                                                 | 84 |

| 5.7  | Profile-aware Safe RAEP-based IntraDVS                                                                                          | 86  |

|------|---------------------------------------------------------------------------------------------------------------------------------|-----|

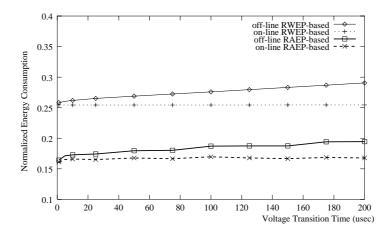

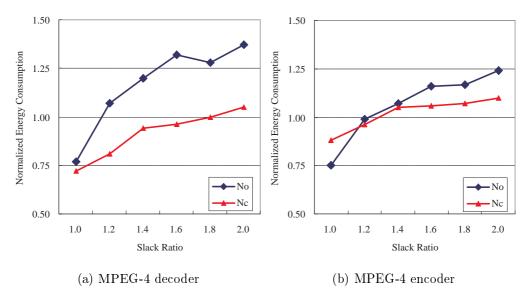

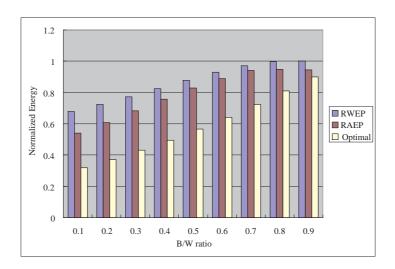

| 5.8  | Normalized starting speed and energy consumption of the RWEP-based IntraDVS and the RAEP-based IntraDVS versus the slack factor | 89  |

| 5.9  | Experimental results of the RWEP-based IntraDVS, the RAEP-based IntraDVS and the optimal DVS                                    |     |

| 5.10 | An example program for look-ahead IntraDVS                                                                                      | 91  |

| 5.11 | An example program for multi-step look-ahead IntraDVS                                                                           | 96  |

| 5.12 | Multi-step LaVSP search algorithm                                                                                               | 98  |

| 5.13 | Overhead in LaIntraDVS                                                                                                          | 99  |

| 5.14 | An example program for L-type VSP                                                                                               | 101 |

| 5.15 | Code transformation: loop splitting                                                                                             | 104 |

| 5.16 | Code transformation: function inlining                                                                                          | 105 |

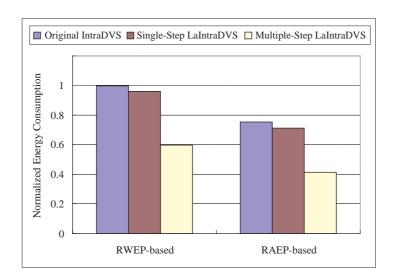

| 5.17 | The framework for look-ahead IntraDVS                                                                                           | 106 |

| 5.18 | Experimental results of look-ahead IntraDVS                                                                                     | 107 |

| 6.1  | Cases where pure InterDVS or pure IntraDVS performs poor.                                                                       | 109 |

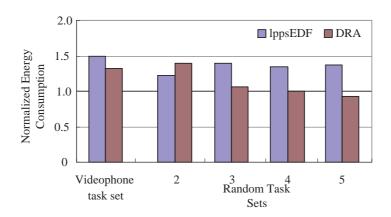

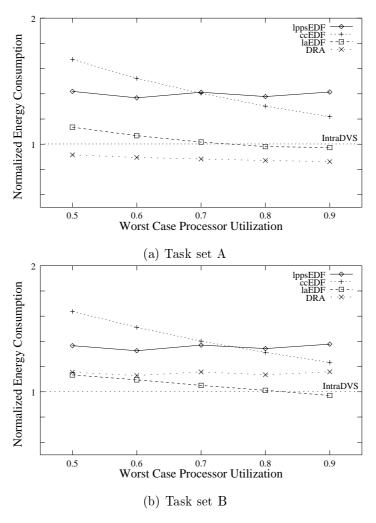

| 6.2  | Energy efficiency comparison results of the HybridDVS algo-                                                                     |     |

|      | rithms                                                                                                                          | 114 |

| 6.3  | Spectrum of HybridDVS heuristics                                                                                                | 115 |

| 8 1  | Dynamic voltage and frequency scaling traces                                                                                    | 138 |

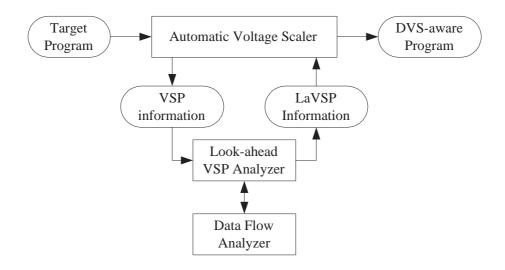

| 8.2 Automatic Voltage Scaler. |  | 141 |

|-------------------------------|--|-----|

|-------------------------------|--|-----|

# List of Tables

| 1.1 | A typical videophone application    | 4   |

|-----|-------------------------------------|-----|

| 2.1 | Variable voltage processors         | 14  |

| 4.1 | DVS experiments on Itsy.            | 60  |

| 4.2 | Management code overhead            | 60  |

| 6.1 | Heuristics for HybridDVS algorithms | 111 |

## Glossary

**ACEP** (Average-Case Execution Path): An execution path which has the highest probability to be executed.

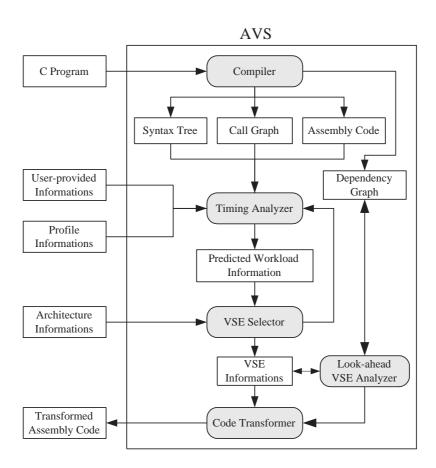

**AVS** (Automatic Voltage Scaler): A software tool which converts a normal program into a DVS-enabled program.

B-type VSE: A VSE for the slack time generated at a branch statement.

**Data flow analysis**: A program analysis technique which provides global information about how a program manipulates its data. Using data flow analysis, we can know where a variable is defined and used.

**Data predecessor**: A statement which assigns a value to be used at a specified program location for a specified variable.

**Down-VSE**: A VSE where clock speed and voltage level are lowered.

**Hybrid DVS**: A DVS algorithm which uses both the intra-task voltage scheduling and the inter-task voltage scheduling.

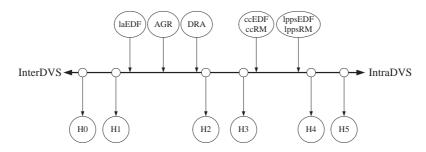

**InterDVS**: A DVS algorithm which schedules the supply voltage between tasks.

**IntraDVS**: A DVS algorithm which schedules the supply voltage within task boundary.

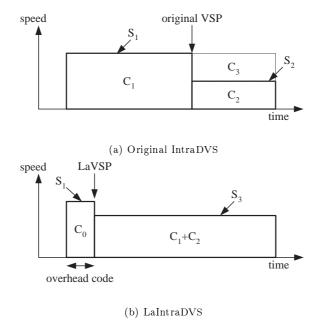

LaIntraDVS (Look-ahead IntraDVS): An Intra-task DVS algorithm which

selects voltage scaling points using data flow analysis.

**LaVSP** (Look-ahead Voltage Scaling Point): A voltage scaling point determined by Look-ahead IntraDVS.

**Look-ahead point**: An earliest program point from which until a specified program location the values of specified variables are not changed.

L-type VSE: A VSE for the slack time generated at a loop statement.

**RAEC** (Remaining Average-case Execution Cycles): A number of cycles required to execute the average-case execution path starting from a specified point.

**RAEP** (Remaining Average-case Execution Path): An execution path which has the highest probability to be executed among the paths starting from a specified point.

Reference Path: An execution path whose execution cycles are used to determine the clock speed in IntraDVS.

**RPEC** (Remaining Predicted Execution Cycles): A number of cycles required to execute the predicted execution path starting from a specified point.

**RWEC** (Remaining Worst-case Execution Cycles): A number of cycles required to execute the longest execution path starting from a specified point. **RWEP** (Remaining Worst-case Execution Path): An execution path which has the longest execution cycles among the all paths starting from a specified point.

**Slack Factor**: A value representing how much static slack times a task has comparing its WCET and deadline. (deadline-WCET)/deadline.

**SUR** (Speed Update Ratio): A ratio between two clock speeds before and after voltage scaling edge.

**Up-VSE**: A VSE where clock speed and voltage level are raised.

Variable-voltage processor: A processor where the clock speed and supply voltage can be adjusted.

**VSE** (Voltage Scaling Edge): A program location where the clock speed and voltage is adjusted.

WCEC (Worst-Case Execution Cycles): A number of cycles required to execute the worst-case execution path.

**WCEP** (Worst-Case Execution Path): An execution path which has the longest execution cycles among the all paths starting from the program entry.

WCET (Worst-Case Execution Time): An execution time required to execute the worst-case execution path.

WCPU (Worst-Case Processor Utilization): A maximum system utilization assuming that all tasks demand the worst-case execution cycles.

Workload-variation slack time: Dynamic slack time. A slack time generated dynamically when a task execution time is smaller than its worst-case execution time.

Worst-case slack time: Static slack time. A extra time identified statically when the worst-case processor utilization is smaller than 1.

# Chapter 1

### Introduction

#### 1.1 Motivation

Recently, the reduction of energy consumption is emerging as a key technology in the VLSI system design, especially for battery-powered portable systems such as digital cellular phones, personal digital assistants, and mobile videophones. For these systems, the low energy consumption is a primary design goal, since the battery operation time is one of the most significant performance measures. Even for non-portable VLSI systems such as high performance microprocessors, the energy consumption is an important design constraint, because large heat dissipations in high-end microprocessors often result in the device thermal degradation, system malfunction, or in some cases, non-recoverable crash. These problems demand low-power technologies over a wide range of hardware and software design abstractions, including device, circuit, logic, architecture, compiler, operating system,

and application levels. Recently, there have been many researches on the system or software-level low-power techniques using compiler and operating systems because the opportunities for power reduction at such levels are larger than those of hardware-level techniques.

Dynamic voltage scaling (DVS) [1] is one of the most effective approaches in reducing the power consumption of embedded systems, where supply voltage can be dynamically reduced to the lowest possible extent that ensures a proper operation when the required performance of the target system is lower than the maximum performance. Since the dynamic energy consumption of CMOS circuits, which dominates total power consumption, is proportional to the square of the supply voltage  $V_{dd}$ , a significant energy reduction is possible with the DVS scheme. Recently, many commercial variable-voltage microprocessors (e.g., [2, 3, 4]) have been introduced to the mobile embedded market, reflecting the effectiveness of DVS techniques.

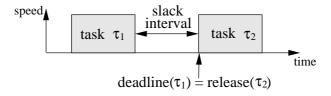

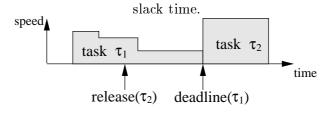

In the past, various OS-level voltage scheduling algorithms have been proposed for hard real-time systems [5, 6, 7, 8, 9, 10, 11, 12]. Given multiple tasks, these algorithms assign the proper speed to each task dynamically while guaranteeing all their deadlines. In real-time systems, since the real execution time of each task may smaller than the worst-case execution time (WCET), workload-variation slack times [13] are generated at run time even though the worst-case utilization of the processor is 1. However, it is difficult to utilize the workload-variation slack times because we cannot know the exact amount of slack time before the completion of a task. Therefore, most of DVS scheduling algorithms [7, 8, 10, 11, 12] transfer the slack time to the following tasks which can utilize it. These techniques exploit the "slack estimation and distribution" strategy for the supply voltage determination,

which can be summarized as follows:

- 1. run the current task.

- 2. estimate the slack time due to early completion of the current task.

- 3. distribute the slack time to the next tasks and determining the operating speed of the tasks.

- 4. run the next tasks.

These techniques determine the supply voltage on *task-by-task basis*. For each task activation, only one supply voltage is assigned to the task, and it is not changed during the task execution. In this paper, we call these techniques as *inter-task dynamic voltage scheduling* (InterDVS).

While generally effective in reducing energy consumption of multi-task real-time systems, InterDVS has several practical limitations. For example, since a task scheduler in OS determines the supply voltage of a task, it requires OS modifications. Furthermore, it cannot be applied to a single-task environment because there is no another task which can utilize the slack time generated by the completed task. Considering many small-size embedded mobile applications are based on a single-task model, this can be detrimental to a wide adoption of variable-voltage processors in practice.

Even in a multi-task environment, InterDVS may not be effective in reducing the energy consumption if one task is dominant in both the slack times and execution times. In this case, a dominant task (with the highest energy consumption) exploits slack times from other tasks (with small slack times), thus ineffective in reducing the energy consumption. For example,

Table 1.1: A typical videophone application.

|                              |                               | MPEG4 Video | MPEG4 Video | VSELP Speech | VSELP Speech |

|------------------------------|-------------------------------|-------------|-------------|--------------|--------------|

|                              |                               | Encoding    | Decoding    | Encoding     | Decoding     |

| Period (= Deadline) (msec)   |                               | 66.667      | 66.667      | 40.000       | 40.000       |

| WCE                          | WCET (msec)                   |             | 9.826       | 1.844        | 1.383        |

| Average Execu                | Average Execution Time (msec) |             | 1.460       | 0.907        | 0.680        |

| Energy InterDVS [8]          |                               | 0.826       |             |              |              |

| Consumption Off-line Optimal |                               | 0.106       |             |              |              |

<sup>\*</sup>In normalizing energy consumption values, the base case of normalization is DVS-unaware systems using only power-down mode.

consider a typical mobile videophone application with four tasks shown in Table 1.1. Using an InterDVS algorithm of [8], only 17% of energy reduction is observed while an off-line (theoretical) optimal voltage scheduling can achieve 90% power reduction<sup>1</sup>.

The limitations of InterDVS algorithms come from their slack estimation techniques. InterDVS estimates a task's workload-variation slack time at the completion of the task. However, it may be too late if there is no or small task workload to exploit the slack time as shown in the videophone application. Therefore, we need a new voltage scheduling technique which can identify the workload-variation slack time instantly during the task execution.

$<sup>^{1}</sup>$ The energy reduction by the InterDVS algorithm of [8] was estimated using a simulation. The off-line optimal schedule was calculated by assuming that the real execution times of tasks are known *a priori*.

#### 1.2 Dissertation Goals

In this dissertation, we are to provide voltage scheduling algorithms which can identify the workload-variation slack time within task boundary. The scheduling algorithm should reduce the energy consumption of real-time tasks guaranteeing the timing constraints of them. Our goals can be described as follows:

- Proposing new voltage scheduling algorithms which can identify and exploit workload-variation slack times of a task during the task execution.

- Optimizing the proposed voltage scheduling algorithms to improve the energy performance.

- Integrating the proposed voltage scheduling algorithms with OS-level InterDVS algorithms.

- Providing an automatic conversion tool that converts DVS-unaware programs into DVS-aware ones based on the proposed voltage scheduling algorithms.

- Examining the energy performance of the proposed voltage scheduling algorithms comparing with other voltage scheduling algorithms.

#### 1.3 Contributions

This dissertation proposes the voltage scheduling technique called the *intra-task dynamic voltage scheduling* (IntraDVS) because it adjusts the voltage

and clock speed within a task. The technique identifies the slack time generated from the workload variation and adjusts the clock/voltage to utilize the slack time at run time. To enable the run-time clock/voltage adjustment, the application code is preprocessed based on the static timing analysis. The workload-variation slack times are identified by observing the changes of the remaining execution times due to the control flow. Specifically, we present:

- A new IntraDVS algorithm using static timing analysis. The algorithm, entitled RWEP-based IntraDVS [14], finds the voltage scaling points from a target program and determines the clock speed at the points. It uses the worst-case timing analysis technique to know the static timing information of the target program. The proposed IntraDVS algorithm has the following features: (1) It fully exploits all workload-variation slack times, achieving a significant improvement in the energy consumption. (2) It is applicable to a single-task environment, since it controls the supply voltage within each task. (3) It provides an automatic conversion tool that converts DVS-unaware programs into DVS-aware ones. This means that a programmer requires no knowledge on DVS, making the proposed algorithm very practical. (4) It enables each individual task to control supply voltage independent of other tasks, without any support from operating systems. Therefore, it can be directly applied to a conventional DVSunaware OS without any modification.

- An extension of the IntraDVS algorithm using profile information.

The algorithm, entitled **RAEP-based IntraDVS** [15], determines

the clock speed based on the average-case execution information guaranteeing the timing constraint of the target program.

- An extension of the IntraDVS algorithm using data flow analysis. The algorithm, called **Look-ahead IntraDVS**, optimizes the locations of scaling points by searching the earliest points where we can detect the change of workload using a data flow analysis technique.

- Techniques for cooperation with InterDVS algorithms. We propose **Hybrid IntraDVS** [16] algorithms which cooperate with the Inter-DVS technique to balance the slack consumption among tasks.

- A software tool for IntraDVS techniques. Based on the proposed IntraDVS algorithms, we developed a software tool called Automatic Voltage Scaler (AVS) that automatically converts a DVS-unaware program into an equivalent low-energy program.

### 1.4 Dissertation Structure

The dissertation has seven chapters and two appendices. The first chapter is this introduction. The last chapter offers conclusions and describes avenues for future work. The five intermediate chapters address the following.

Chapter 2 provides the background for real-time systems and dynamic voltage scaling. We introduce the worst-case timing analysis technique for real-time systems, which is closely related to our work. The fundamental relations between clock frequency, supply voltage, power and energy are described. We also serves the related works on dynamic voltage scheduling.

Chapter 3 describes the overall algorithm of the proposed IntraDVS and the formulation of IntraDVS problem.

Chapter 4 presents details of the IntraDVS algorithm which uses the static timing analysis technique. We describe how to select the voltage scaling points and how to transform a target program to make a DVS-aware program.

Chapter 5 describes two improvement techniques for IntraDVS, using the execution profile information and using the data flow analysis.

Chapter 6 shows how to cooperate for IntraDVS with OS-level InterDVS algorithms. We show that there are cases where the pure IntraDVS or the pure InterDVS dose not work well and propose hybrid IntraDVS techniques which use both IntraDVS and InterDVS.

Appendix provides the information about several variable-voltage processors and the detail description about the automatic voltage scaler, the software tool for IntraDVS.

# Chapter 2

# Background

### 2.1 Real-Time Systems

Real-time systems are considered to be those types of systems which have to respond to certain stimuli within a finite and specified delay. In other words, the correctness such systems depends not only on the logical result of the computations, but also on the time at which the results are produced. For hard real-time systems, it is imperative that responses occur within the specified deadline, any exception leading to a total failure of the system. In soft real-time systems, response times are important, but the system will still function correctly if some deadlines are occasionally missed.

Various scheduling techniques have been proposed to ensure that tasks finish before their deadlines. These scheduling algorithms generally require that the worst-case execution time (WCET) of each task in the system be known a priori. The worst-case execution time is a possible longest

execution time of a program code on a given hardware. The WCET of a task depends on many factors including the source code of a target application, the target machine's architectural features, compiler and operating system, etc. There have been several researches focusing on the estimation of the WCETs of tasks. The estimation of WCET must be safe and accurate. The safeness means that the estimated WCET is not shorter than the real WCET. The accuracy means that the estimated WCET is close to the real WCET. An accurate and safe estimation of a task's WCET is crucial for reasoning about the timing properties of real-time systems.

One of most popular static WCET analysis techniques is to use a timing schema [17]. In this approach, we first build the control flow graph of basic blocks of a program. Next, we determine the time of each basic block by adding up the execution time of the machine instructions. Finally, we determine the WCET of a whole program by using timing schema. The timing schema is a set of formulas for computing execution time bounds of language constructs. For example, consider a conditional statement

$$S: \mathbf{if}(E)$$

then  $S_1$ ; else  $S_2$ .

We can represent the WCET of the statement S, WCET(S), as

$$WCET(E) + max(WCET(S_1), WCET(S_2))$$

assuming a simple single-issue architecture without pipeline and cache for the target machine.

However, for modern RISC processors, such timing information is not sufficient to accurately account for timing variations resulting from pipelined execution and cache memory. So, there have been intensive studies about the WCET estimation for modern processors [18, 19, 20]. Especially, Lim et al. [21] proposed an extended timing schema of RISC processors, which models pipeline and cache. Using the timing schema, they built a timing analysis tool. We use the timing analysis tool for our IntraDVS algorithms to know the static timing information of a target program.

### 2.2 Dynamic Voltage Scaling

#### 2.2.1 Power and Energy

In order to design energy-efficient systems, one has to understand first the sources of energy consumption. It is also important to examine the relations between power, energy, and signal delay in digital CMOS circuits. The power dissipated on a CMOS circuit can be decomposed into two basic types, static and dynamic [22]:

$$P_{CMOS} = P_{static} + P_{dynamic} (2.1)$$

In the ideal case, CMOS circuits do not dissipate static power, since in steady state there is no open path from source to ground. In reality, there are always leakage currents and short circuit currents which yield the static component of the CMOS power consumption. Although the static power is today about two orders of magnitude smaller than the total power, the typical chip's leakage power increases about 5 times each generation, and will soon become a significant portion of the total power [23].

The dynamic component of the CMOS power is dissipated during the

transient behavior, i.e. during switching between logic levels and is represented as following equation:

$$P_{dynamic} = \alpha \cdot C_L \cdot V_{dd}^2 \cdot f_{clk} \tag{2.2}$$

$\alpha$  is the switching activity factor (the average number of high-to-low transitions in one clock period),  $C_L$  is the load capacitance,  $V_{dd}$  is the supply voltage and  $f_{clk}$  is the clock frequency. In CMOS circuits, this component of power dissipation accounts for at least 85-90% of the total power consumption [22].

From all the considerations made above, we can approximate the power dissipated on a CMOS circuit node using the following equation:

$$P_{CMOS} \approx P_{dynamic} = \alpha \cdot C_L \cdot V_{dd}^2 \cdot f_{clk} = C_{eff} \cdot V_{dd}^2 \cdot f_{clk}$$

(2.3)

where  $C_{eff}$  is the effective load capacitance.

This means that the power consumption in a CMOS circuit is proportional to the switching activity, capacitive load, clock frequency, and the square of the supply voltage. All the power and energy reduction techniques try to minimize one or more of these factors. Especially, supply voltage  $(V_{dd})$  reduction appears to be the most promising, because of its quadratic dependency to power. A decrease in voltage by a factor of two yields a decrease in power by a factor of four. We call the technique which adjust the supply voltage to minimize the power consumption as the dy-namic voltage scaling.

In this dissertation, we focus on energy rather than power consumption. Although low power and energy efficiency are often perceived as overlapping goals, there are certain differences when designing for one or the other. Formally, the energy consumed by a system is the amount of power used during a certain period of time. We can denote the energy consumption E during the time interval T as follows:

$$E = \int_0^T P(t)dt \propto V_{dd}^2 \cdot f_{clk} \cdot T = V_{dd}^2 \cdot N_{cycle}$$

(2.4)

P(t) is the power consumption at the time t and  $N_{cycle}$  is the number of clock cycles during the time interval T. Equation (2.4) tells that reducing only the clock frequency makes no change in the energy consumption (though it reduces the power dissipation).

Unfortunately, we can not reduce the supply voltage for free. The circuit delay  $\Delta$ , which sets the clock frequency, depends on the supply voltage [24]:

$$\frac{1}{f_{clk}} \propto \Delta \propto \frac{V_{dd}}{(V_{dd} - V_t)^{\gamma}} \tag{2.5}$$

where  $V_t$  is the threshold voltage and  $\gamma$  is the saturation velocity index ( $\gamma$  is between 1 and 2.). For a sufficiently small  $V_t$  we can rewrite the relation between clock frequency and supply voltage as:

$$f_{clk} \propto V_{dd}^{(\gamma-1)} \tag{2.6}$$

For this reason supply voltage and clock frequency should be scaled together. Consequently, dynamic voltage scaling provides the energy reduction but lead to a slow system. Real-time scheduling and energy minimization are therefore closely related problems, that should be tackled in conjunction for best results.

Table 2.1: Variable voltage processors.

|            | Processor              | Clock Range                 | Voltage Range | Transition Time                                      |

|------------|------------------------|-----------------------------|---------------|------------------------------------------------------|

|            | Transmeta Crusoe [26]  | $200-700\mathrm{MHz}$       | 1.1 - 1.65V   | $300 \mu \mathrm{s}$                                 |

|            | AMD Mobile K6 [3]      | $192 - 588 \mathrm{MHz}$    | 0.9 - 2.0V    | $200 \mu \mathrm{s}$                                 |

| Commercial | Intel PXA250 [4]       | $100-400\mathrm{MHz}$       | 0.85 - 1.3V   | $500 \mu \mathrm{s}$                                 |

|            | IBM PowerPC 405LP [27] | $152-380\mathrm{MHz}$       | 1.0 - 1.8V    | $400 \mu \mathrm{s}$                                 |

|            | Compaq Itsy [28]       | $59.0 - 206.4 \mathrm{MHz}$ | 1.0 - 1.55V   | $189 \mu \mathrm{s}$                                 |

|            | TI TMS320C55x [25]     | $6-200\mathrm{MHz}$         | 1.1 - 1.6V    | $300 \mu s (1.1 \to 1.6 V)$                          |

|            |                        |                             |               | $3.3m\mathrm{s}(1.6 \rightarrow 1.1V)$               |

|            | UC Berkely lpARM [1]   | $5-80\mathrm{MHz}$          | 1.2 - 3.8V    | $70 \mu \mathrm{s}$                                  |

| Academic   |                        |                             |               | $140\mu\mathrm{s}(59\leftrightarrow221\mathrm{MHz})$ |

|            | TU Delft LART [29]     | $59-221\mathrm{MHz}$        | 0.8 - 1.5V    | $40\mu\mathrm{s}(0.8 	o 1.5V)$                       |

|            |                        |                             |               | $5.5ms(1.5 \rightarrow 0.8V)$                        |

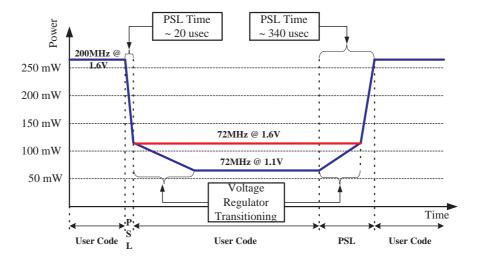

### 2.2.2 Variable-Voltage Processors

Recently, many variable-voltage processors have been announced. Table 2.1 shows the representative commercial variable-voltage processors and academic trials to implement variable-voltage processors. These processors provide finite numbers of voltage and clock levels within the voltage/clock range specified. Each processor requires a time delay to change the voltage/clock level. Most of variable-voltage processors except Transmeta's Crusoe provide the software mechanisms for users to be able to control the voltage and clock level such as TI's Power Scaling Library [25]. Appendix A contains the detail descriptions of variable-voltage processors. Throughout this dissertation, we make the following assumptions on a target variable-voltage processor:

1. The processor provides a special instruction, change\_f\_V( $f_{clk}$ ), that dynamically controls clock frequency  $f_{clk}$  and its corresponding voltage  $V_{dd}$  of the processor based on Equation (2.6).

- 2.  $f_{clk}$  and  $V_{dd}$  have continuous values within the operational range of the processor.

- 3. When the processor changes  $(f_{clk1}, V_{dd1})$  to  $(f_{clk2}, V_{dd2})$ , there is a clock/voltage transition overhead period of  $C_{VTO}$  cycles<sup>1</sup>.

- 4. During clock/voltage transition, the processor stops running.

Assumptions (1), (3) and (4) are valid for most of variable processors. Especially, assumption (4) is conservative considering recent variable-voltage processors such as TI's TMS320C55x which stops during the clock transition but operates during the voltage transition. Assumption (2) is not realistic because most of variable-voltage processors provide only discrete voltage/clock levels. However, our work can support the processors with a finite number of voltage/clock levels with a slight modification of speed selection algorithm.

Generally, dynamic voltage scaling is applied only to processor and onchip memory (on-chip cache). Other peripherals and external memory have their own clock frequencies different from internal processor frequency and sustain the clock frequencies despite of the clock scaling of processor. In this dissertation, we consider only the processor's energy consumption and assume that the system performance is proportional to the processor's clock frequency. The DVS techniques considering other external devices as well

<sup>&</sup>lt;sup>1</sup>The clock/voltage transition time is different depending on the source voltage and the target voltage. However, we assumed there is a fixed voltage transition time for a simple explanation. Since we represent the fixed clock/voltage transition overhead period by the number of cycles, it can vary depending on the current clock frequency. For a simpler analysis, we assume that  $C_{VTO}$  cycles were counted under the maximum clock frequency.

as processor is one of our future works.

#### 2.3 Related Works

For hard real-time systems where timing constraints must be strictly satisfied, a fundamental energy-delay tradeoff makes it more challenging to adjust the supply voltage dynamically while minimizing the energy consumption and guaranteeing the timing requirements. For this reason, extensive studies have been recently carried out on the DVS problems. For hard real-time systems, there are two kinds of voltage scheduling approaches depending on the voltage scaling granularity: intra-task DVS (IntraDVS) and inter-task DVS (InterDVS). The intra-task DVS algorithms [14, 30] adjust the voltage within an individual task boundary, while the inter-task DVS algorithms determine the voltage on a task-by-task basis at each scheduling point. The main difference between them is whether the slack times are used for the current task or for the tasks that follow. InterDVS algorithms distribute the slack times from the current task for the following tasks, while IntraDVS algorithms use the slack times from the current task for the current task itself.

### 2.3.1 InterDVS Algorithms

The InterDVS algorithms are classified depending on slack estimation method. Slack times generally come from two sources; worst-case slack times are the extra times identified statically when the worst-case processor utilization is smaller than 1, while workload-variation slack times are caused from run-

time variations of the task executions.

The worst-case slack estimation methods is to compute the speed of each task, which is defined as the clock speed to minimize the energy consumption guaranteeing the feasible schedule of a task set [5, 6, 31, 30, 32]. For example, in EDF scheduling, if the worst case processor utilization (WCPU) U of a given task set is lower than 1.0 under the maximum speed  $f_{max}$ , the task set can be scheduled with the speed  $f = U \cdot f_{max}$ .

Even though a given task set is scheduled such that there are no worst-case slack times, since the actual execution times of tasks are usually much less than their WCETs, the tasks usually have workload-variation slack times. One simple method to estimate the workload-variation slack time is to use the arrival time of the next task [8, 31]. (The arrival time of the next task is denoted by NTA.) Assume that the current task  $\tau$  is scheduled at time t. If NTA of  $\tau$  is later than  $(t+\text{WCET}(\tau))$ , task  $\tau$  can be executed at a lower speed so that its execution completes exactly at the NTA.

In the priority-driven scheduling such as RM and EDF, we can exploit the basic properties of the scheduling to estimate workload-variation slack times. The basic idea is that when a higher-priority task completes its execution earlier than its WCET, the following lower-priority tasks can use the slack time from the completed higher-priority task. It is also possible for a higher-priority task to utilize the slack times from completed lower-priority tasks. However, the latter type of slack stealing is computationally expensive to implement precisely. Therefore, the existing algorithms are based on heuristics [10, 12].

Another method is to use the processor utilization. The actual processor

utilization during run time is usually lower than the worst case processor utilization. We can estimates the required processor performance at the current scheduling point by recalculating the expected worst case processor utilization using the actual execution times of completed task instances [11]. When the processor utilization is updated, the clock speed can be adjusted accordingly. The main merit of this method is its simple implementation, since only the processor utilization of completed task instances have to be updated at each scheduling point. Kim et al. [33] evaluated the energy efficiencies of state-of-the-art InterDVS algorithms.

There have been studies on InterDVS for special configurations. Im et al. [34] proposed an InterDVS technique for multimedia applications. Their algorithm fully utilizes the idle intervals with buffers in a variable speed processor and determines the minimum buffer size to achieve the maximum energy saving. The energy performance of the technique is strongly dependent on the available buffer size. This technique has a limitation that it can be used only when a system can buffer multiple input data or output results.

Hong et al. [35] have proposed a set of heuristic algorithms to schedule a mixed workload of periodic and sporadic tasks. Their algorithm optimizes the energy consumption while ensuring that all periodic tasks meet their deadlines and accept as many sporadic tasks, which can be guaranteed to meet their deadlines, as possible.

Shin and Kim [36] have proposed scheduling algorithms for the systems which have both periodic tasks and aperiodic tasks. The algorithms tries to minimize the energy consumption guaranteeing the timing constraints

of periodic tasks while bounding the maximum increase of aperiodic tasks' response time. They exploited the behaviors of the bandwidth-preserving servers [37] for aperiodic task scheduling such as deferrable server, sporadic server, total bandwidth server and constant bandwidth server.

#### 2.3.2 IntraDVS Algorithms

Comparing with InterDVS techniques, few approaches have been introduced for IntraDVS techniques. Lee and Sakurai [13] proposed an intra-task voltage scheduling where each task is partitioned into fixed-length segments. After the completion of each segment, the supply voltage is adjusted depending on the slack time made by the previous segment. This is the same idea of InterDVS if we regard the segment as a task. Although [13] shows a significant improvement in the energy reduction, it provides no systematic methodology for developing DVS-aware intra-task applications. For example, there exists no systematic guideline of selecting the best program locations where voltage scaling code is inserted. Consequently, the programmer himself should find out proper locations based on his own knowledge. It implies that the technique described in [13] is very difficult to be applied to practical applications, since average programmers are generally not familiar with low-energy software issues as well as timing analysis techniques.

Another approach of IntraDVS is based on the stochastic method [30, 38]. This technique is motivated by the idea that it is usually better to start at low speed and accelerate execution later when needed than to start at high speed and reduce the speed later when the slack time is found in the program execution. However, it requires the probability density function of execution

times of a task to calculate the optimal speed schedule. Furthermore, the stochastic IntraDVS requires OS modification like InterDVS and cannot utilize all the slack times. In Chapter 4, we compare the energy efficiency of the stochastic IntraDVS technique with our proposed IntraDVS techniques.

Hsu and Kremer [39] also proposed a different kind of IntraDVS. While our IntraDVS estimates the slack times of a task based on the changes of the remaining execution cycles due to the control flow, their technique finds the slack times based on the architectural characteristic of microprocessor. By identifying the program regions in which the CPU is mostly idle due to memory stalls, their technique slows down the clock speed of CPU in the regions for energy reduction with negligible performance loss. However, this technique should be carefully used in real-time systems due to the performance degradation. Since this technique is different from our IntraDVS in the kind of slack times exploited, it can be used together with our IntraDVS for a better energy performance.

# Chapter 3

# Intra-Task Voltage Scheduling Framework

#### 3.1 Basic Idea

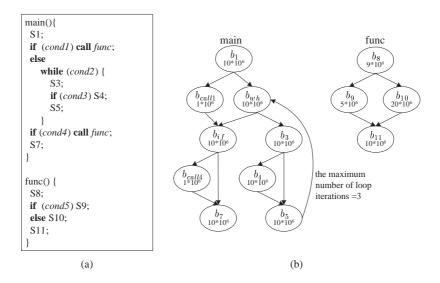

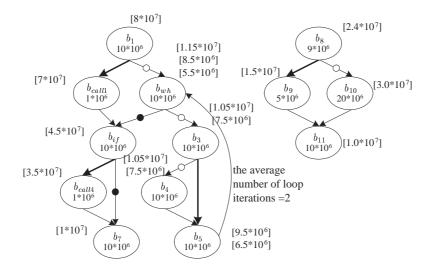

Consider a hard real-time program P with the deadline of 2 sec shown in Figure 3.1(a). The control flow graph (CFG)  $G_P$  of the program P is shown in Figure 3.1(b). In  $G_P$ , each node represents a basic block of P and each edge indicates the control dependency between basic blocks. The number within each node indicates the number of execution cycles of the corresponding basic block. The back edge from  $b_5$  to  $b_{wh}$  models the **while** loop of the program P.

In developing hard real-time systems where tasks have strict timing constraints (i.e., deadlines), the worst-case execution times (WCETs) of the tasks are estimated in advance (prior to run time) to guarantee that re-

quired timing constraints are met. Such WCETs can be predicted by existing analysis tools that produce safe and accurate prediction results [40, 21]. Using a WCET analysis tool, we can find the path  $p_{worst} = (b_1, b_{wh}, b_3, b_4, b_5, b_{wh}, b_3, b_4, b_5, b_{wh}, b_5, b_{wh}, b_6, b_{wh}, b_6, b_{wh}, b_6, b_{wh}, b_6, b_{wh}, b_6, b_{wh}, b_{if}, b_{call4}, b_8, b_{10}, b_{11}, b_7)$  as the worst-case execution path (WCEP) for the example program P, assuming that the maximum number of **while** loop iterations is set to 3 by user. The predicted execution cycles of  $p_{worst}$  is, therefore,  $200 \times 10^6$  cycles<sup>1</sup>, which is the worst-case execution cycles (WCEC). If a target processor operates at the maximal clock frequency of 100 MHz, the program P completes its execution in 2 sec, resulting in no slack time.

However, there are large execution time variations among different execution paths. In particular, the average-case execution paths (ACEPs) complete their executions much earlier than the WCEP(s) does [8]. For the example program shown in Figure 3.1(b), there exist 51 different execution paths. While the WCEP  $p_{worst}$  takes  $200 \times 10^6$  cycles, twelve of 51 possible execution paths take less than  $100 \times 10^6$  cycles. For such short execution paths, the workload-variation slack times are generated. If we were able to identify them in the early phase of its execution, we can lower the clock speed substantially, thus saving a significant amount of energy consumption. Consider the path  $p_1 = (b_1, b_{call1}, b_8, b_9, b_{11}, b_{if}, b_{call4}, b_8, b_{10}, b_{11}, b_7)$  of Figure 3.1(b) whose execution takes  $95 \times 10^6$  cycles. In the ideal case, we can start the execution with the clock speed of 47.5 MHz without violating

<sup>&</sup>lt;sup>1</sup>For simple explanations, we assume that the number of execution cycles for an execution path is the sum of all basic blocks' execution cycles. This is true when the target machine is a single issue architecture without pipeline and cache. However, our algorithms can be used for any architecture if there is a timing analysis tool for the architecture.

Figure 3.1: An example program P: (a) an example real-time program with the 2 sec deadline and (b) its CFG representation  $G_P$

the 2 sec deadline, if we can perfectly predict that the actual execution path will be  $p_1$  before the processor starts  $b_1$ . Unfortunately, we do not generally know in advance which execution path will be taken by the next program execution. Therefore, we cannot start with the 47.5 MHz clock speed, although this will improve the energy efficiency significantly.

The solution for this problem is to adjust the clock speed within the task depending on the workload-variations. For example, when the program control flow follows the execution path  $p_1$  of Figure 3.1(b), we can reduce the clock speed at edge  $(b_1, b_{call1})$  because we know this control flow dose not follow the WCEP. In the proposed IntraDVS algorithm, we identifies the appropriate program locations where the clock speed should be adjusted, and inserts clock and voltage scaling codes to the selected program locations at compile time. The branching edges of the CFG, i.e., branch or loop

statements, are the candidate locations for inserting voltage scaling codes because where the changes of remaining execution cycles are occurred.

# 3.2 Problem Modeling

We consider a real-time task  $\tau$  with the deadline D. The task  $\tau$  is represented by its CFG  $G_{\tau}$ . If the task  $\tau$  has N number of basic blocks,  $b_1, b_2, \dots, b_N$ ,  $G_{\tau}$  consists of N nodes. (We assume that  $b_1$  is the entry basic block of the task  $\tau$ .) We associate each basic block  $b_i$  with its basic block information (BBI) structure. The BBI structure BBI( $b_i$ ) of the basic block  $b_i$  consists of three entries:  $C_{EC}(b_i)$ ,  $S(b_i)$ , and  $E(b_i)$ .  $C_{EC}(b_i)$  denotes the number of clock cycles<sup>2</sup> needed to execute  $b_i$ .  $S(b_i)$  represents the processor speed in clock frequency at which  $b_i$  is executed.  $E(b_i)$  is defined as  $C_{EC}(b_i) \cdot S(b_i)^2$  by Equation (2.4). (We assume the supply voltage is proportional to the clock speed.)  $E(b_i)$  is the relative energy consumption during the execution of  $b_i$ .

Similar notations are defined for execution paths.  $p_i$  denotes an execution path of a task  $\tau$ .  $p_i$  can be expressed as a sequence of basic blocks.  $C_{EC}(p_i)$  represents the number of execution cycles when  $p_i$  is executed. For paths, we use a notation  $\Phi^{b_i}$  which means the set of all the partial execution paths starting from basic block  $b_i$ .

<sup>&</sup>lt;sup>2</sup>Note that BBI definition above is represented in execution cycles, instead of execution time. This is because, as we adjust the clock speed on a variable-voltage processor, the execution time is changing for a given basic block, but the number of execution cycles remains constant. Given the number of execution cycles, the execution time can be computed by multiplying the clock cycle time.

The IntraDVS algorithm is to find how much we should change the clock speed at each edge  $(b_i, b_j)$  in the CFG of a target program to minimize the total energy consumption of the program satisfying the timing constraint of the program. That is, we should find the value  $r_{i,j} = S(b_j)/S(b_i)$  for each edge  $(b_i, b_j)$ . We call this ratio a speed update ratio (SUR). For an execution path  $p_m = (b_1, \dots, b_{n_m})$ ,  $S(b_i)$  can be represented as

$$S(b_i) = S_0 \cdot \prod_{k=1}^{i} r_{k-1,k} \quad (S(b_i) \ge S_{min} \text{ and } S(b_i) \le S_{max}),$$

(3.1)

where  $S_0$  is the initial clock speed at the start of a program and  $S_{min}$  ( $S_{max}$ ) is the minimum (maximum) value of the clock speed provided by the target variable-voltage processor. We can also denote  $E(b_i)$  as

$$E(b_i) = C_{EC}(b_i) \cdot S(b_i)^2 = C_{EC}(b_i) \cdot (S_0 \prod_{i=1}^{i} r_{k-1,k})^2.$$

(3.2)

Then, the energy consumption during the execution of the path  $p_m$  is proportional to

$$E(p_m) = \sum_{i=1}^{n_m} E(b_i) = \sum_{i=1}^{n_m} \left( C_{EC}(b_i) \cdot (S_0 \prod_{i=1}^{n} r_{k-1,k})^2 \right).$$

(3.3)

From this formula, we can represent the target function to minimize as

$$\sum_{\forall p_m \in \Phi^{b_1}} E(p_m) \cdot prob(p_m) = \sum_{\forall p_m \in \Phi^{b_1}} \left[ \sum_{i=1}^{n_m} \left( C_{EC}(b_i) \cdot (S_0 \prod_{i=1}^{i} r_{k-1,k})^2 \right) \cdot prob(p_m) \right] (3.4)$$

$prob(p_m)$  is the probability that the path  $p_m$  is executed among all the paths in  $\Phi^{b_1}$ .

There is a timing constraint for this problem. Since the target program  $\tau$  should be completed before the deadline D, we can denote the timing constraint as

$$\forall p_m, \sum_{i=1}^{n_m} \frac{C_{EC}(b_i)}{S(b_i)} = \sum_{i=1}^{n_m} \frac{C_{EC}(b_i)}{S_0 \prod_{i=1}^{i} r_{k-1,k}} \le D.$$

(3.5)

Using a simple inference, we can conclude the optimal solution satisfies

$$\forall p_m, \sum_{i=1}^{n_m} \frac{C_{EC}(b_i)}{S_0 \prod_{i=1}^{i} r_{k-1,k}} = D, \quad \forall p_m, \sum_{i=1}^{n_m} \frac{C_{EC}(b_i)}{D \prod_{i=1}^{i} r_{k-1,k}} = S_0.$$

(3.6)

So,  $S_0$  can be estimated when  $r_{i,j}$  for each edge  $(b_i, b_j)$  is determined.

Since the formula (3.4) is a non-linear equation for  $r_{i,j}$ , this problem is a Non-Linear Program (NLP) problem. Generally, there is no polynomial time algorithm for NLP problem. So, we propose an heuristic algorithm similar to the gradient descent method.

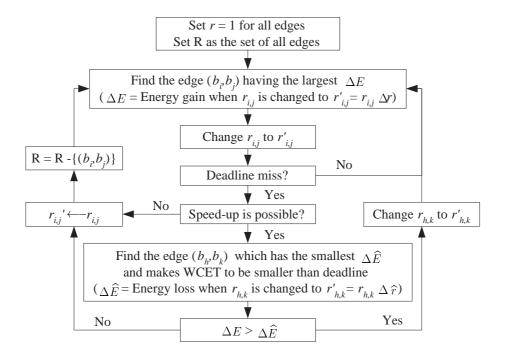

Figure 3.2 shows the heuristic search algorithm. For each  $r_{i,j}$ , we set the initial value of it to 1, which means there is no speed update at the corresponding edge, and constitute the set R which has all edges in  $G_{\tau}$  of the target program. We change  $r_{i,j}$  as the amount of  $\Delta r$ , which is a very small number between 0 and 1, during the successive iterations in Figure 3.2. In each iteration, we first find the edge  $(b_i, b_j)$  having the largest  $\Delta E$ .  $\Delta E$  means the energy gain when the  $r_{i,j}$  is changed to  $r'_{i,j} = r_{i,j} \cdot \Delta r$ . From the formula (3.1), we can represent  $\Delta E$  as

$$\Delta E(r_{i,j}) = S_0 \cdot (1 - \Delta r^2) \cdot \sum_{p_m \in \Phi^{b_j}} prob(p_m) \sum_{k=j}^{n_m} C_{EC}(b_k) \cdot S(b_k)^2.$$

(3.7)

After we change the value of  $r_{i,j}$ , we should check whether the timing constraint of formula (3.5) is satisfied in spite of the increased execution time of  $p_m$ . If there is no deadline miss, we try again the same process.

When there is a deadline miss, we can choose two kinds of approaches. First approach is to admit no speed-up, that is, SURs are always smaller than 1. In this case, the clock speed only decreases as a target program executes. So, there is no chance to solve the deadline miss problem by increasing the clock speed at an edge after  $(b_i, b_j)$ . We should restore  $r'_{i,j}$  to  $r_{i,j}$  and eliminate the corresponding edge  $(b_i, b_j)$  from the set of candidate edges, R. Second approach is to admit speed-up. In this case, since the clock speed can be increased by an edge after  $(b_i, b_j)$ , we can decrease  $r_{i,j}$  despite of the deadline miss. To maintain the selected edge  $(b_i, b_j)$  in R, we should find the other edge, say  $(b_h, b_k)$ , which has the smallest  $\Delta \widehat{E}$ .  $\Delta \widehat{E}$  means the energy loss when the  $r_{h,k}$  is changed to  $r'_{h,k} = r_{h,k}\Delta \widehat{r}$   $(\Delta \widehat{r} > 1)$ . After we change  $r_{h,k}$ , the potential energy gain should be checked whether  $\Delta E$  is larger than  $\Delta \widehat{E}$ . If there is no edge satisfying such a condition, we restore  $r'_{i,j}$  to  $r_{i,j}$  and eliminate the corresponding edge  $(b_i, b_j)$  from R.

This heuristic algorithm shows following features: (1) The nearest edge from the entry basic block is first selected from R because it has the largest value of  $\Delta E$ . After the corresponding SUR of the selected edge is fixed, the following edges are processed. (2) The nearest edge from the exit basic block is first selected to increase its SUR. (3) In the constraint that SURs should be smaller than 1,  $S(b_i)$  is determined to be close to the value under

Figure 3.2: The heuristic search algorithm for IntraDVS problem.

which the target processor can execute  $MAX_{p_j \in \Phi^{b_i}}(C_{EC}(p_j))$  cycles until the deadline.  $MAX_{p_j \in \Phi^{b_i}}(C_{EC}(p_j))$  is the remaining worst-case execution cycle of  $b_i$ . Namely, the SURs are optimal to the remaining worst-case execution path. (4) Without such a constraint, the SURs are determined so that the average energy consumption is minimized satisfying the deadline constraint. In this case, the determined speed is near to the optimal speed value for the average-case execution path.

# 3.3 Voltage Scheduling Using Reference Path

The algorithm shown in Figure 3.2 has several problems. First, it requires a significant computation time. The computation time is proportional to the number of basic blocks and execution paths. Considering that general programs have at least hundreds of basic blocks, it is difficult to use the algorithm for real applications. Second, we should insert voltage scaling codes at most of edges in a program. This introduces a significant increase in code size. Therefore, we need more efficient algorithms.

From the features of the heuristic algorithm, we can modify the algorithm to the less complex algorithm. We predict an execution path which the control flow will follow. There can be several methods how to predict the execution path. A simple method is to use the WCEP. Once the execution path is predicted, we set the initial clock frequency and its corresponding voltage assuming that the task execution will follow the predicted execution path. We call the predicted execution path as the reference path because the clock speed is determined based on the execution path.

When the actual execution deviates from the (predicted) reference path (say, by a branch instruction), the clock speed can be adjusted depending on the difference between the remaining execution cycles of the reference path and that of the newly deviated execution path. If the new execution path takes significantly longer to complete its execution than the reference execution path, the clock speed should be raised to meet the deadline constraint. On the other hand, if the new execution path can finish its execution earlier than the reference execution path, the clock speed can be lowered to save the energy consumption. Once the actual execution takes a different path from the reference path, a new reference path is constructed starting from the deviated basic block.

In actual implementation of the IntraDVS, we do not need to maintain the reference path. To implement the IntraDVS algorithm efficiently, we identifies the appropriate program locations where the clock speed should be raised or lowered relative to the current clock speed using a static program-analysis technique. For run-time clock speed adjustment, it inserts voltage scaling codes to the selected program locations at compile time. The branching edges of the CFG, i.e., branch or loop statements, are the candidate locations for inserting voltage scaling codes because where the prediction miss for the reference path can be occurred. They are called as *Voltage Scaling Edges* (VSEs) because the clock speed and voltage are adjusted at these edges. At each VSE  $(b_i, b_j)$ , the clock speed is determined by the predicted remaining execution cycles (RPECs) of  $b_i$ ,  $C_{RPEC}(b_j)$ . The value of  $C_{RPEC}(b_j)$  depends on the prediction algorithm.

There are two issues in the IntraDVS. One is how to predict the reference path. Depending on the prediction method, the IntraDVS framework can be implemented into different IntraDVS algorithms. In this dissertation, we adopt two kinds of reference paths, i.e. remaining worst-case execution path (RWEP) and remaining average-case execution path (RAEP). Based on the prediction method, there are two different algorithms, i.e. RWEP-based IntraDVS and RAEP-based IntraDVS. In the former, the clock speed is monotonically decreased at all the VSEs. This is correspond to the case speed-up is not admitted. On the contrary, in the latter, the clock speed may be increased as well at some VSEs. In this case, we classify VSEs into Up-VSEs and Down-VSEs. The clock speed is increased at an Up-VSE while it is decreased at a Down-VSE.

The second issue is how to select VSEs. This is to determine the voltage scaling points in the program code. The optimal points are the earliest points where we can detect the changes of the remaining predicted execution cycles. We use two kinds of selection algorithms, one is to use only the control flow information and the other is to use the data flow information in addition. Selecting VSEs, the timing overhead due to voltage transition and inserted codes should be considered. We provide the solutions for these issues in Chapters 4 and 5.

# Chapter 4

# IntraDVS Using Static Timing Analysis

# 4.1 RWEP-based IntraDVS Algorithm

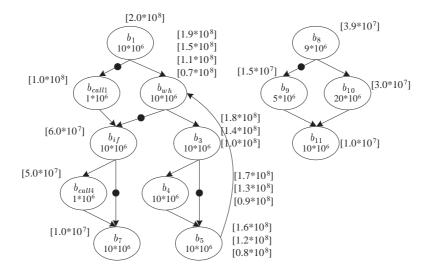

In the RWEP-based IntraDVS, we use the remaining worst-case execution cycles (RWECs)  $C_{RWEC}(b_i)$  for the predicted remaining execution cycles. This guarantees that all possible execution paths meet the deadline. Figure 4.1 shows an augmented CFG  $G_P^{RWEP}$  with  $C_{RWEC}(b_i)$  values for the RWEP-based IntraDVS. Using the static timing analysis tools, we can compute  $C_{RWEC}(b_i)$  for each basic block  $b_i$  and construct the graph  $G_P^{RWEP}$  statically. To compute the worst-case execution cycles, we use follow equa-

Figure 4.1: A RWEP-based CFG  $G_P^{RWEP}$ .

tions:

$$S: \mathbf{if}(E)$$

then  $S_1$ ; else  $S_2$ .

$WCEC(S) = WCEC(E) + max(WCEC(S_1), WCEC(S_2))$

$S: \mathbf{while}(E)$   $S_1$ .

$WCEC(S) = (WCEC(E) + WCEC(S_1)) \cdot N_{max} + WCEC(E)$

where  $N_{max}$  means the maximum number of loop iterations.

For the basic blocks related to the **while** loop (i.e.,  $b_{wh}$ ,  $b_3$ ,  $b_4$ ,  $b_5$ ), the corresponding nodes are associated with multiple  $C_{RWEC}(b_i)$  values, reflecting the maximum three iterations of the **while** loop.

With the graph  $G_P^{RWEP}$ , we can identify VSEs that drops the remaining worst-case execution cycles *faster* than the current execution rate. For example, in Figure 4.1, five VSEs are identified, i.e.,  $(b_1, b_{call1})$ ,  $(b_{wh}, b_{if})$ ,  $(b_{if}, b_7)$ ,  $(b_3, b_5)$  and  $(b_8, b_9)$ . In Figure 4.1, these edges are marked by the

symbol •. When the thread of execution control branches to the next basic block through one of VSEs, say  $(b_1, b_{call1})$ , the clock speed can be lowered because the remaining work is reduced by the difference between  $C_{RWEC}(b_{wh})$  and  $C_{RWEC}(b_{call1})$ . By reducing the clock speed so that the  $C_{RWEC}(b_{call1})$  cycles can be completed exactly at the deadline, the proposed technique always meets the required timing constraint. Since the voltage scaling decisions are made at compile time, there exists no run-time overhead directly related to the selection of voltage scaling edges. In addition, the compile-time static analysis procedure does not require special programmer's interventions other than ones typically required in developing normal hard real-time programs (e.g., the maximum number of loop iterations).

At the entry basic block  $b_1$ , the starting speed is set to  $C_{WCEC}/D$ , where  $C_{WCEC}$  is the worst-case execution cycles of the whole program. When we denote  $C_{RWEC}(t)$  as the remaining worst-case execution cycles at time t,  $C_{RWEC}(t)$  is linearly decreased at the rate of clock speed along with the program execution, as far as the execution follows the worst-case execution path  $p_{worst}$ . However, if the execution deviates from the basic block  $b_i$  in the worst-case execution path  $p_{worst}$  to other basic block  $b_j$  not included in  $p_{worst}$ ,  $C_{RWEC}(t)$  drops by the difference between  $C_{RWEC}(b_i) - C_{EC}(b_i)$  and  $C_{RWEC}(b_j)$  after the execution of  $b_i$  is completed. Then, we adjust the clock speed at the time t, S(t) as follows:

$$S(t) = \frac{C_{RWEC}(t)}{(D-t)} \tag{4.1}$$

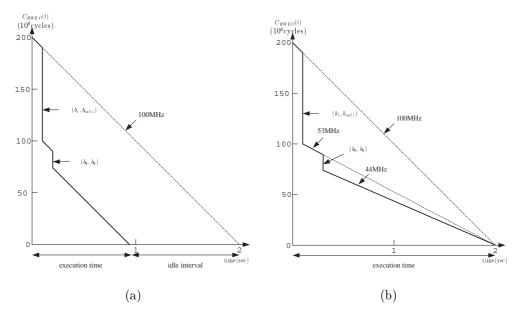

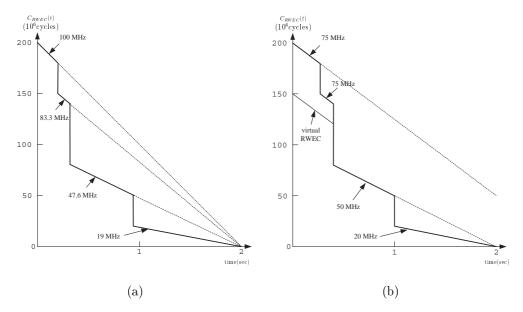

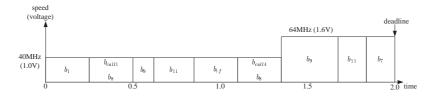

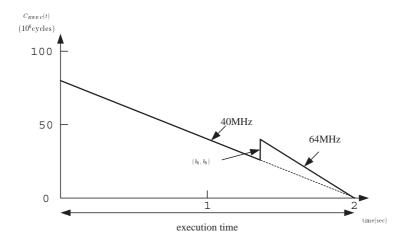

Figure 4.2 shows how  $C_{RWEC}(t)$  dynamically changes as the path  $p_1=(b_1, b_{call1}, b_8, b_9, b_{11}, b_{if}, b_{call4}, b_8, b_{10}, b_{11}, b_7)$  of the example program P shown in Figure 4.1 is executed. In Figure 4.2(a) where no speed scheduling is

Figure 4.2: The changes of  $C_{RWEC}(t)$  over different speed scaling algorithms: (a) no IntraDVS and (b) RWEP-based IntraDVS.

used,  $C_{RWEC}(t)$  drops at two edges,  $(b_1, b_{call1})$  and  $(b_8, b_9)$ . Since no speed scheduling is used,  $C_{RWEC}(t)$  is decreased at the rate of 100 MHz, resulting in a slack time interval of 1.05 sec. Figure 4.2(b) shows the effect of speed scheduling for the same execution path assuming there is no voltage transition overhead. When the remaining worst-case execution cycles drops, the minimum processor speed that can complete the remaining program execution before the deadline also drops. Thus, processor speed is changed from 100 MHz to 53 MHz when  $C_{RWEC}(t)$  drops right after the execution of  $b_1$  is completed. When  $C_{RWEC}(t)$  drops right after  $b_8$ , speed is also changed due to the same reason.  $C_{RWEC}(t)$  is dropped vertically at VSEs in Figure 4.2. The number of the reduced cycles of  $C_{RWEC}(t)$  at VSEs is denoted as  $C_{saved}$ .

**Theorem 1** If we can use any real value of clock frequency f,  $0 < f \le f_{max}$ , at a variable-voltage processor and there is no overhead time during the clock and voltage transition, the execution time of a task scheduled by the IntraDVS algorithm with a relative deadline D is exactly D when  $WCEC/f_{max} \le D$ .

Proof. The task starts with the initial speed WCEC/D. Assume the task meets a VSE at time t but meets no VSE after the time t. The IntraDVS algorithm sets the clock speed S(t) such that

$$S(t) = \frac{C_{RWEC}(t)}{(D-t)}$$

as shown in Equation (4.1).  $C_{RWEC}(t)$  is smaller than or equal to the following value:

$$WCEC - t \cdot \frac{WCEC}{D}$$

So,

$$S(t) = \frac{C_{RWEC}(t)}{(D-t)} \le \frac{WCEC}{D} \le f_{max}.$$

Therefore, we can use the clock speed of S(t) at time t. Then, the execution time of the task is

$$t + \frac{C_{RWEC}(t)}{S(t)} = t + (D - t) = D.$$

Theoretically, since the IntraDVS can fully exploit all workload-variation slack times, all of task executions are completed exactly at the deadline. However, some slack time can be generated in real variable-voltage processors even though we use the IntraDVS technique. This is because variable-voltage processors provide only finite numbers of clock/voltage levels and

require voltage transition times to change the clock/voltage level. These two factors prevent IntraDVS from adjusting the clock/voltage level at all VSE candidates (i.e., branching edges).

Figure 4.3 compares how the speed and voltage change depending on whether the IntraDVS is used or not. Assume that no energy is consumed in an idle state. When the execution follows the path  $p_1$ , the energy consumption ratio of Figure 4.3(b) to Figure 4.3(a) is 0.288. With the IntraDVS, the energy consumption is reduced by 71.2%.

# 4.2 Selection of Voltage Scaling Edges

To adjust the clock speed and voltage at run time, the voltage scaling edges should be selected at compile time considering the saved cycles and the

Figure 4.3: Speed and voltage changes: (a) without IntraDVS and (b) with the RWEP-based IntraDVS

overhead cycles. Observing its behavior, VSEs are classified into B-type VSEs and L-type VSEs.

# 4.2.1 B-type Voltage Scaling Edges

A B-type VSE corresponds to the CFG edge between two basic blocks that are part of conditional statements such as the if statement. For the if statement, the WCET is predicted to be the larger of two execution times, one for the then path and the other for the else path. Assume that the condition of the if statement is evaluated in  $b_{cond}$ , the then path starts from  $b_{then}$  and the else path starts from  $b_{else}$ . If the condition of the if statement evaluates to true and the then path is shorter than the else path,  $C_{RWEC}(t)$  is decreased by  $(C_{RWEC}(b_{else}) - C_{RWEC}(b_{then}))$ . In this case, the speed can

be decreased before the  $b_{then}$  block is executed by a ratio of  $\frac{C_{RWEC}(b_{then})}{C_{RWEC}(b_{else})}$ . This value is a SUR and is represented by  $r(b_{cond}, b_{then})$ .

In adjusting clock/voltage at VSEs, several instructions are required other than voltage-changing instruction (change\_f\_V( $f_{clk}$ )). We denote the number of cycles needed for these extra instructions at a B-type VSE as  $C_{VSO_B}$ . The total number of overhead cycles  $C_{overhead_B}$  for a B-type VSE, therefore, is given by  $C_{VTO} + C_{VSO_B}$ . The SUR  $r(b_i, b_j)$  for a B-type VSE  $(b_i, b_j)$  is calculated as follows:

$$r(b_i, b_j) = \frac{C_{RWEC}(b_j)}{C_{RWEC}(succ_{worst}(b_i)) - C_{overhead_B}}$$

(4.2)

where  $succ_{worst}(b_i)$  is the basic block  $b_k$  that is an immediate successor of  $b_i$  and has the largest  $C_{RWEC}(b_k)$  among all the successors of  $b_i$ . If  $C_{RWEC}(b_j) \geq C_{RWEC}(succ_{worst}(b_i)) - C_{overhead_B}$ , that is  $r(b_i, b_j) \geq 1$ , the edge  $(b_i, b_j)$  is not selected as a VSE. For a VSE between  $b_i$  and  $b_j$ , a SUR  $r(b_i, b_j)$  is multiplied to the current speed before  $b_j$  starts its execution. For example, assuming  $C_{overhead_B}$  as 0,  $S(b_{call1})$  in Figure 4.1 is changed from 100 MHz to 53 MHz (=100 MHz  $\times \frac{100 \times 10^6}{190 \times 10^6}$ ).

**Theorem 2** Using the IntraDVS algorithm with the speed update rule in Equation (4.2), the execution time of a task with the relative deadline D is no more than D at a variable-voltage processor which provides continuous clock frequency f such that  $0 < f \le f_{max}$ .

*Proof.* Assume that a task has the worst-case execution cycles W. If the control flow meets a VSE  $(b_i, b_j)$  at the time t and  $succ_{worst}(b_i)$  is  $b_k$ , the

speed is changed to

$$S(b_j) = S(b_i) \cdot \frac{C_{RWEC}(b_j)}{C_{RWEC}(b_k) - C_{overhead_B}}$$

where  $S(b_i) \leq f_{max}$ . Since there is no voltage transition at the edge  $(b_i, b_k)$ ,  $S(b_i)$  is same to  $S(b_k)$ . Assume that

$$S(b_i) = S(b_k) = C_{RWEC}(b_k)/(D - t - \delta)$$

$$(4.3)$$

where  $(\delta \geq 0)$ . If the first clock/voltage transition occurs at the VSE  $(b_i, b_j)$ , this assumption is true because  $S(b_i) = W/D$  and  $C_{RWEC}(b_k) = W \cdot (D - t)/D$ . For the cases where  $(b_i, b_j)$  is not the first VSE, the assumption will be shown to be true using  $S(b_j)$ .

Then, we can rewrite  $S(b_j)$  as follows:

$$S(b_j) = \frac{S(b_i) \cdot C_{RWEC}(b_j)}{S(b_i) \cdot (D - t - \delta) - C_{overhead_R}}$$

(4.4)

During the clock and voltage transition, there is the overhead time  $C_{overhead_B}/f_{max}$ . If the VSE  $(b_i, b_j)$  is the last VSE which the task meets during execution, the completion time is as follows:

$$t + \frac{C_{overhead_B}}{f_{max}} + \frac{C_{RWEC}(b_j) \cdot (S(b_i) \cdot (D - t - \delta) - C_{overhead_B})}{S(b_i) \cdot C_{RWEC}(b_j)}$$

$$= t + \frac{C_{overhead_B}}{f_{max}} + (D - t - \delta) - \frac{C_{overhead_B}}{S(b_i)}$$

$$= D - (\delta + C_{overhead_B} \cdot (\frac{1}{S(b_i)} - \frac{1}{f_{max}})) \le D$$

$$(4.5)$$

If the task execution meets another VSE  $(b_u, b_v)$  after  $(b_i, b_j)$  at time t' and  $succ_{worst}(b_u)$  is  $b_w$ ,

$$S(b_j) = \frac{C_{RWEC}(b_j)}{D - t - (\delta + \frac{C_{overhead_B}}{S(b_i)})} = \frac{C_{RWEC}(b_j)}{D - t - \delta'}$$

(4.6)

$$C_{RWEC}(b_w) = C_{RWEC}(b_w) - (t'-t) \cdot S(b_i)$$

$$(4.7)$$

From Equations (4.6) and (4.7),

$$S(b_j) = \frac{C_{RWEC}(b_w)}{(D - t' - \delta')} = S(b_w)$$

(4.8)

From Equation (4.8), we can know that the assumption of Equation (4.3) is true. Consequently, we can conclude that the execution time is smaller than D.

### 4.2.2 L-type Voltage Scaling Edges

Although WCEC is predicted assuming that a loop will be iterated by the user-provided maximum number of loop iterations, the loop is generally iterated smaller times than the maximum loop bound. In this case, slack time occurs and clock speed can be scaled down. We call this type of scaling L-type scaling. L-type VSEs correspond to the loop-exit edges in a CFG. In the L-type scaling, the number of saved cycles  $C_{saved}$  for a loop l is given by

$$C_{saved}(l) = C_{WCEC}(l) \cdot (N_{worst}(l) - N_{exec}(l)) \tag{4.9}$$

where  $C_{WCEC}(l)$  is the number of worst-case execution cycles to execute the loop l once,  $N_{worst}(l)$  is the number of user-provided maximum loop bound value for the loop l, and  $N_{exec}(l)$  is the number of actual loop iterations measured at run time. Consider the edge  $(b_{wh}, b_{if})$  in Figure 4.1. Assuming  $N_{exec}(l) = 1$ , and  $C_{overhead_L} = 0$ ,  $S(b_{if})$  is updated as follows:

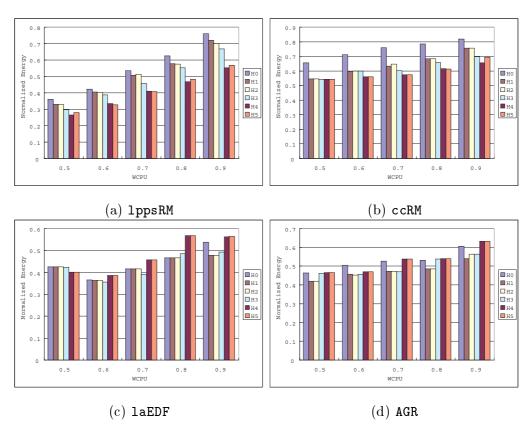

$$S(b_{if}) = S(b_{wh}) \cdot \frac{C_{RWEC}(b_{if})}{C_{RWEC}(b_{if}) + C_{saved}(l) - C_{overhead_L}}$$